1M-Byte RAM im GENIE III

Helmut BerhardtEinbauanleitung für das 256K-(1M-) Banking-Board

(siehe: 256K RAM für Z80-Systeme)

Wegen nicht vorhandener Hardware-Dokumentation werden hier für den GENIE III alle wichtigen Informationen zum Umrüsten auf 256K, 512K oder 1M RAM zusanmengestellt.

Das Banking-Board wird dabei in geeigneter Weise unter dem CPU-Board angebracht und die Verbindungen zwischen den Boards werden mit dünnen isolierrten Drahtlitzen hergestellt. Bei den meisten Leitungen können die Enden der Litzen direkt auf der Lötseite an die entsprechenden Pins der ICs gelötet werden.

Verbindungen zu Pins von Huckepack-ICs müssen durch Bohrlöcher, die an geeigneter Stelle im CPU-Board angelegt werden, geführt werden. Wenn man das Board gegen das Licht hält, sieht man freie Stellen, wo auf beiden Seiten keine Leiterbahnen verlaufen.

Es sollte darauf geachtet werden, daß die Drahtverbindungen mölichst kurz sind.

Im einzelnen sind folgde Maßnahmen durchzufühen:

- Sämtliche 4116-RAMs werden durch 41256-RAMs ersetzt

- Auf der Bestückungsseite wird die breite unter Z8 (74LS00) hindurchführende Leiterbahn (+12V) durchtrennt.

- Auf der Lötseite wird die außen an den ROM-Sockeln vorbeiführende und mit "-5V" beschriftete Leiterbahn durchtrennt.

- Auf der Lötseite wird die Verbindung zwischen Pin16 von 212 (74LS161) zu Pin9 des RAMs daneben durchtrennt.

- Auf der Lötseite wird die breite Leiterbahn (neben der mit "-5V" beschrifteten Leiterbahn) zwischen dem Widerstandsarray und dem Kondensator, neben dem auf der Bestückungsseite "D0" steht, durchtrennt.

- Zwischen Pin8 des obersten linken (bestückungsseitig gesehen) RAMs und dem äußersten linken Pin des Widerstandsarays wird mit einem nicht zu dünnen isolierten Draht eine Verbindung hergestellt.

- Im Bereich der RAMs werden alle auf dem Bestückungsplan eingekreisten Kondensatoren ausgelötet.

- Auf der Bestückungsseite werden die 4 nebeneinander verlaufenden Leiterbahnen von den Pins 4-7 von Z17 (74LS139) zu den Pins 2, 5, 10 und 13 von Z21 (74LS32) durchtrennt.

- Auf der Lötseite wird die zu Pin3 von Z23 (74LS157) führende Leitung (A7)

durchtrennt. Dieser Pin wird mit Pin7 von Z20 (74LS244) verbunden.

Auf der Lötseite wird die von Pin3 von Z23 unter den ICs 26 und 30 hindurch zu Pin1 des Sockels von EP3 führende Leiterbahn durchtrennt. Der Pin1 von EP3 wird mit A7' des Bankers verbunden. - Auf Z23 (74LS157) wird ein zusätzliches IC 74LS157 mit d Rins 1, 8, 15 und 16 huckepack-aufgelötet (gleiche Orientierung); alle anderen Pins werden waagerecht abgebogen. An die Pins 2 und 3 des Huckepack-ICs werden A16 und A17 des Banking-Boards geführt. Pin 4 wird über einen 33-Ohm-Widerstand mit den Pins 1 der RAMs (vorher -5V) verbunden. An Pin5 wird A7' und an Pin6 wird A15' des Banking-Boards geführt. Pin7 wird über einen 33-Ohm-Widerstand mit den Pins 9 der RAMs (vorher +5V) verbunden.

- Das Signal CASEN* für das Banking-Board wird von Pin1 von Z17 (74LS139) abgenommen.

- RESET* kann an Pin26 der Z80-CPU abgenommen werden. Wegen der Nutzung des NMI*-Signals zum Booten des DOS ist es aber zweckmäßig, anstelle des reinen RESET* für das Banking-Board lieber ein SYSES-Signal zu erzeugen. Dafür wird auf Z22 (74LSOO) ein 74LS08 mit den Pins 7 und 14 huckepack- aufgelötet. Alle anderen Pins werden hochgebogen. Pin1 dieses ICs wird mit Pin17 des Z80 und Pin2 mit Pin26 des Z80 verbunden. An Pin3 wird das Signal SYSRES* abgenommen, das anstelle von RESET* an das Banking-Board geführt wird.

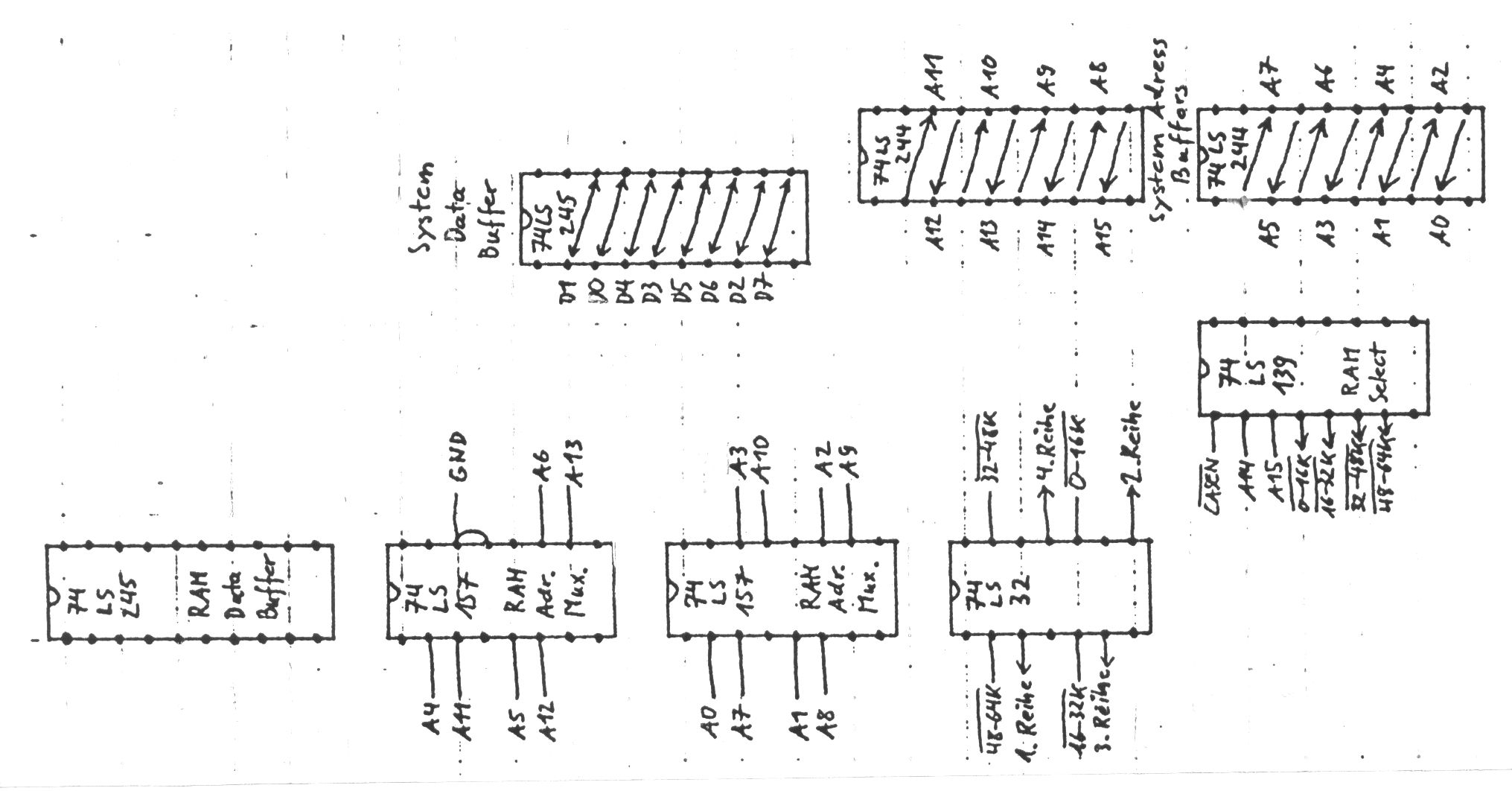

- Die Signale D0-D5, AO-A7 und A15 werden von den im Auszug aus dem Bestückungsplan (Abb.1) bezeichneten Pins des ICs Z25 (74LS245), sowie Z20 und Z16 (74LS244) abgenommen.

- IORQ* wird von Pin3 von Z19 (74LS367), WR* von Pin13 und RFSH* von Pin5 von Z19 (74LS367) abgenommen.

- +5V und GND können von beliebigen ICs in der Nähe der Stelle, wo das Banking-

Board montiert wird, abgenommen werden.

+5V: Z16, 20, 25 und 30 jeweils Pin 20 217, 19, 23 und 26 jeweils Pin 16 Z13, 14, 18, 21, 22 und 24 jeweils Pin 14 GND: Z16, 20, 25 und 30 jeweils Pin 10 Z17, 19, 23 und 26 jeweils Pin 8 Z13, 14, 18, 21, 22 und 24 jeweils Pin 7 - Die Signale CASEN1* bis CASEN4* werden (in dieser Reihenfolge) an die Pins 2,

10, 5 und 13 von Z21 (74LS32) gelegt. Wenn nur 256K realisiert werden sollen,

brauchen diese Siale nicht benutzt zu werden. Dann wird nur die linke Reihe

RAM-Sockel mit 41256-RAMs bestückt und eine Verbindung zwischen Pin2 von Z21

(74LS32) und Pin1 von 217 (74LS139) hergestellt.

Wenn 512K gewünscht sind, werden die beiden linken RAM-Reihen bestückt und CASEN1* an Pin2 und CASEN2* an Pin10 von Z21 (74LS32) geführt. - Wenn das Banking in den oberen 32K des Z80-Adreßraums erfolgen soll, muß ein invertiertes A15 an das Banking-Board geführt werden. Dafür kann ein freies NAND -Gatter von Z8 (74LSOO) verwendet werden. A15 (von Pin9 von Z20, 74LS244) wird an die Pins 12 und 13 von Z8 gelegt und an Pin11 von Z8 kann das invertierte A15 abgenommen werden.

Um das Banking sowohl unter GDOS als auch unter CP/M (und wenn es das mal geben sollte: CPM/M+) nutzen zu können, ist es zweckmäßig, zwischen A15 selbst und dem invertierten A15 mit einem Umschalter wählen zu können.

Da im GENIE III die Ports EOH bis EFH belegt sind, muß für das Banking-Board eine andere Adresse gewählt werden. Geeignet ist die Portadresse DF; dafür sind dann die Adreßleitungen an folgende Punkte anzuschließen:

| A7 an 7 und n | A5 an 8 | A2 an 3 |

| A6 an 6 und m | A4 an 5 | A1 an 2 |

| A3 an 4 | A0 an 1 |

Der Punkt 11 wird mit keinem der Punkte 1-7 verbunden. Die Punkte 9 und 10 werden nicht angeschlossen.

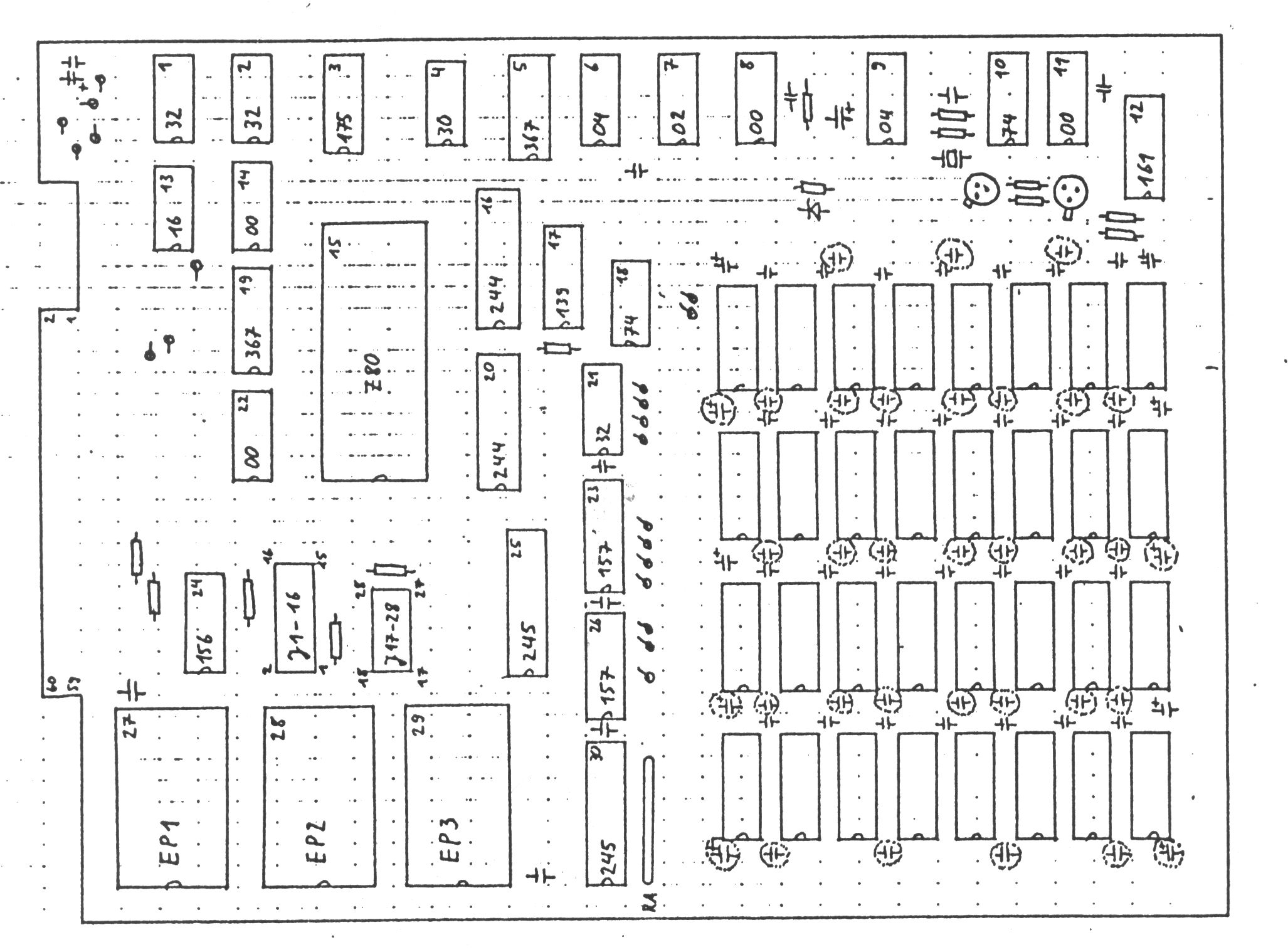

Abb.1: Auszug aus dem Bestückungsplan des GIII Motherboards. Es handelt sich von rechts nach links um die ICs 16, 17, 20, 21, 23, 25, 26, 30 im Bereich zwischen RAMs, EPROMS und CPU.

Abb.2: Bestückungsplan des GIII Motherboards